- 您现在的位置:买卖IC网 > Sheet目录2000 > IDT23S08-1HPGI8 (IDT, Integrated Device Technology Inc)IC CLK MULT PLL HI DRV 16-TSSOP

1

COMMERCIALANDINDUSTRIALTEMPERATURERANGES

IDT23S08

3.3V ZERO DELAY CLOCK MULTIPLIER

MAY 2010

2003

Integrated Device Technology, Inc.

DSC 6394/10

c

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

FEATURES:

Phase-Lock Loop Clock Distribution for Applications ranging

from 10MHz to 133MHz operating frequency

Distributes one clock input to two banks of four outputs

Separate output enable for each output bank

External feedback (FBK) pin is used to synchronize the outputs

to the clock input

Output Skew <200 ps

Low jitter <200 ps cycle-to-cycle

1x, 2x, 4x output options (see table):

– IDT23S08-1 1x

– IDT23S08-2 1x, 2x

– IDT23S08-3 2x, 4x

– IDT23S08-4 2x

– IDT23S08-1H, -2H, and -5H for High Drive

No external RC network required

Operates at 3.3V VDD

Spread spectrum compatible

Available in SOIC and TSSOP packages

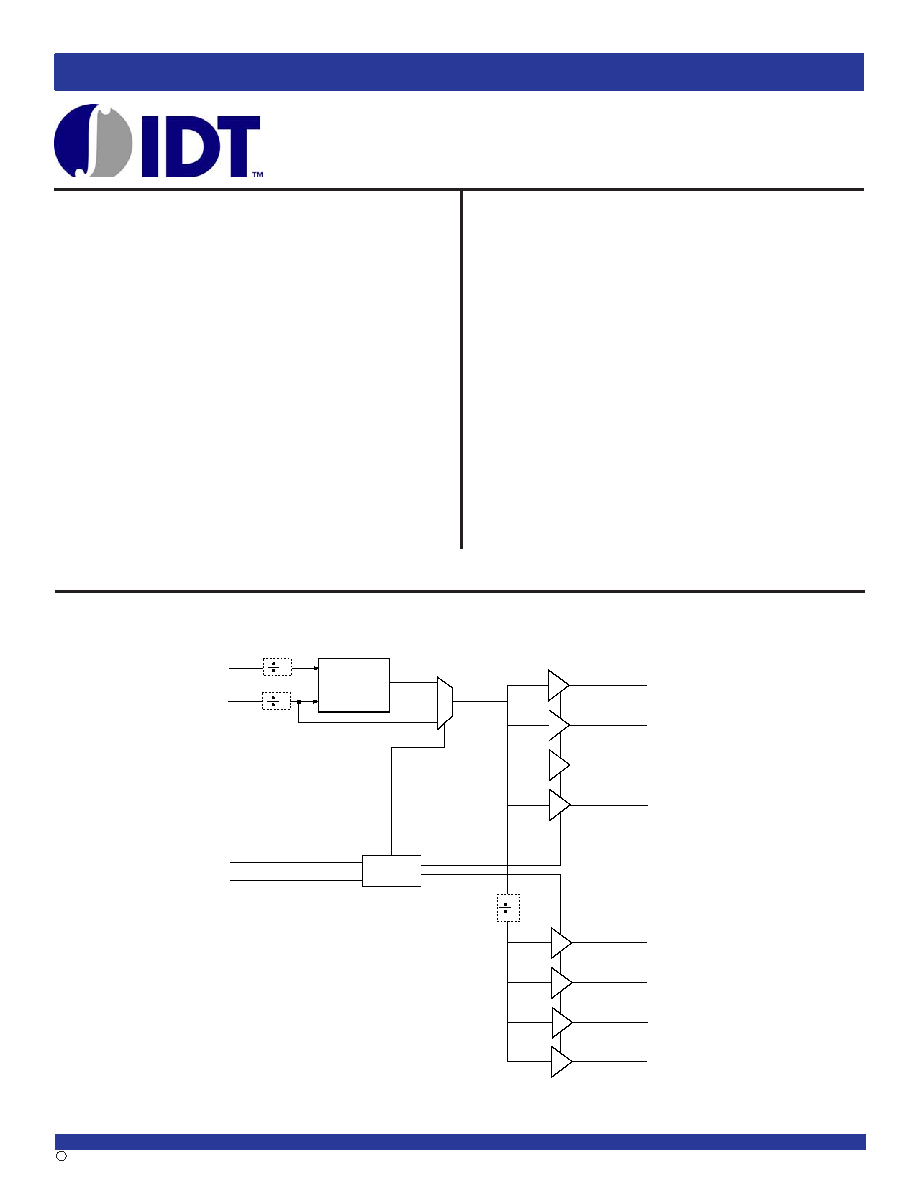

FUNCTIONAL BLOCK DIAGRAM

DESCRIPTION:

The IDT23S08 is a high-speed phase-lock loop (PLL) clock multiplier. It is

designedtoaddresshigh-speedclockdistributionandmultiplicationapplica-

tions.Thezerodelayisachievedbyaligningthephasebetweentheincoming

clock and the output clock, operable within the range of 10 to 133MHz.

TheIDT23S08hastwobanksoffouroutputseachthatarecontrolledviatwo

selectaddresses.Byproperselectionofinputaddresses,bothbankscanbe

put in tri-state mode. In test mode, the PLL is turned off, and the input clock

directly drives the outputs for system testing purposes. In the absence of an

input clock, the IDT23S08 enters power down. In this mode, the device will

drawlessthan12AforCommercialTemperaturerangeandlessthan25A

forIndustrialtemperaturerange,andtheoutputsaretri-stated.

The IDT23S08 is available in six unique configurations for both pre-

scaling and multiplication of the Input REF Clock. (See available options

table.)

ThePLLisclosedexternallytoprovidemoreflexibilitybyallowingtheuser

tocontrolthedelaybetweentheinputclockandtheoutputs.

TheIDT23S08ischaracterizedforbothIndustrialandCommercialopera-

tion.

IDT23S08

3.3V ZERO DELAY CLOCK

MULTIPLIER, SPREAD

SPECTRUM COMPATIBLE

PLL

S1

2

14

15

3

CLKA1

CLKA2

CLKA3

CLKA4

6

10

11

CLKB1

CLKB2

CLKB3

CLKB4

9

FBK

16

Control

Logic

7

8

1

REF

S2

(-2, -3)

(-3, -4)

(-5)

2

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDT23S08T-1DC

IC CLK MULT PLL ZD 2.5V 16-SOIC

IDT23S09T-1DC8

IC CLK BUFFER ZD 2.5V 16-SOIC

IDT5T929-30NLGI

IC CLOCK GENERATOR PREC 28VFQFPN

IDT5T940-10NLGI

IC CLK GENERATOR PREC 28-VFQFPN

IDT5T9820NLI8

IC CLK DRIVER ZD PLL 68-VFQFPN

IDT5T9890NLI8

IC CLK DRIVER 2.5V PLL 68-VFQFPN

IDT5V19EE604NDGI8

IC PLL CLK GEN 200MHZ 28VFQFPN

IDT5V40501DVG

IC CLK GEN PLL 160MHZ 8TSSOP

相关代理商/技术参数

IDT23S08-2

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:3.3V ZERO DELAY CLOCK MULTIPLIER, SPREAD SPECTRUM COMPATIBLE

IDT23S08-2DC

功能描述:IC CLK MULT PLL STD DRV 16-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG

IDT23S08-2DC8

功能描述:IC CLK MULT PLL STD DRV 16-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG

IDT23S08-2DCG

功能描述:IC CLK MULT PLL STD DRV 16-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR)

IDT23S08-2DCG8

功能描述:IC CLK MULT PLL STD DRV 16-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR)

IDT23S08-2DCGI

功能描述:IC CLK MULT PLL STD DRV 16-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR)

IDT23S08-2DCGI8

功能描述:IC CLK MULT PLL STD DRV 16-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR)

IDT23S08-2DCI

功能描述:IC CLK MULT PLL STD DRV 16-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG